秦晓的“国企观”

http://www.gkong.com 2009-07-21 17:25 来源:中国自动化学会专家咨询工作委员会

摘要:与传统的PLC、PAC以及基于PC的系统控制技术不同,嵌入式控制技术可以根据受控对象不同,为我们提供多种选择。微控制器是嵌入式控制技术中最广为人知的一项,而本文将向你展示ASIC和FPGA技术所具有的一些独特优势。

与传统的PLC、PAC以及基于PC的系统控制技术不同,嵌入式控制技术可以根据受控对象不同,为我们提供多种选择。微控制器是嵌入式控制技术中最广为人知的一项,而本文将向你展示ASIC和FPGA技术所具有的一些独特优势。

嵌入式控制系统不同于数据采集系统以及那些只针对标准大众化产品的控制系统。它可以复杂到类似一套电信交换系统,也可以如一套警报系统。在不同的应用中,我们可以采用多种方案来满足不同要求。哪种方案最适合你,一方面由最终的使用情况决定,另一方面取决于系统生命周期。

有三种CPU方案用在嵌入式系统中最为合适。它们分别是:微控制器、现场可编程逻辑门阵列(FPGA)以及专用集成电路(ASIC)。

微控制器的最大优点是它们的高度适应性。开发人员可以通过C以及C++之类的高级语言对它们实施编程。如今,许多微控制器应用已经相当复杂了,以至于我们能够采用Linux或Microsoft Windows Embedded之类的操作系统。

微控制器的高度适应性同时也成为了它们最大的缺陷。微控制器往往需要搭配一套编写复杂、资源全面的操作系统方能使用。在许多应用中,微控制器无法胜任那些对性能要求极高的任务。

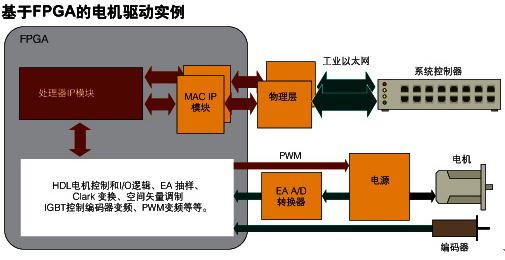

嵌入式控制系统设计师可以利用FPGA和ASIC实现一些非常复杂的算法。这些算法会在结构紧凑的可编程硬件内高速运行。

ASIC和FPGA的特点

如今,我们还可以用另外两种具有计算功能的芯片替代微控制器。它们分别是现场可编程逻辑门阵列(FPGA)以及专用集成电路(ASIC)。两者的共同特点首先是都采用了硬件化的布尔逻辑算法。其次,它们都具有高度的适应性,能够实现相当丰富的逻辑功能。这些功能小到简单的开关控制,大到整个微处理器。再者,它们都可以通过诸如VHDL和Verilog之类的标准硬件描述语言(HDL)进行编程,不必动用由第三代或更高级编程语言编写的软件进行编程。

两者的不同之处在于一次性工程成本(NRE)和可变成本,以及重复编程性、可测量性、开发时间(与产量有关)等方面。

FPGA的特点是能够被重复编程,从而为样品开发提供了便利。此外,我们还能够对FPGA进行产生调整和现场升级,从而加快了产品投放市场的速度。一款FPGA平台适用于多种产品,从而起到了平衡开发成本与资源的作用。如果我们采用ASIC或MCU作设计开发,那么就无法得到这些优势了。

维基百科把FPGA描述成一种包含了可编程逻辑器件(被称为“逻辑模块”)以及可编程互连网络的半导体设备。逻辑模块经过编程后能够实现基本的逻辑门功能,例如与逻辑(AND)和异或逻辑(XOR),以及更复杂的复合逻辑功能,例如解码器或数学运算功能。

ASIC是一种针对某种特殊应用定制的集成电路,它不具有通用性。例如,一款经过专门设计、用来实现手机中某项特定功能的芯片就是一种ASIC。

在设计一款全定制ASIC时,我们必须绘制出设备的整个光刻层。ASIC技术的NRE大部分消耗在将HDL代码转换为半导体结构阶段。

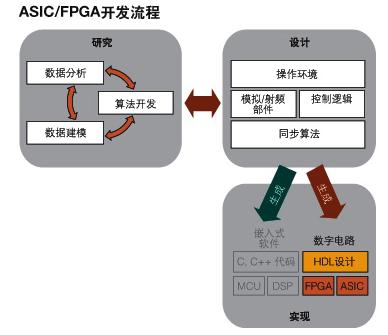

无论是设计FPGA还是ASIC,都要先从编写硬件描述语言(HDL)起步。但是在编写HDL代码之前,我们最好采用软件或硬件仿真的方式来构建、测试并调试整个系统的算法。

算法的开发过程

一般而言,算法最初是作为一种系统工程策略,由用户提出的使用要求所决定。

以一个机器人割草机为例。整个开发项目可能会从一次完整的计算机仿真开始。其中,处于开发阶段的算法(AUD)是由C或C++程序模块组合而成的。 这些模块可能是借用了其他项目的开发成果,也可能是通过另外的多种途径获得的。

这些模块由一套专门的监控程序调用。监控程序的作用是对嵌入式系统软件实行打包操作。它可以在桌面开发系统上运行,而且桌面系统还可以同时运行电机、驱动器、传感器以及图形用户界面的的C或C++仿真模块。

算法开发从一开始就是在计算机上进行的,从而保证算法能够完成预订的功能并且时刻处于开发人员的掌控之中。每一位明智的开发人员都会在确保算法正确,并且不会出现潜在硬件隐患的情况下将它移交给测试工程师。否则,你最终得到的将是一台失控的机器人,就像科幻小说中描述的那样。简直就是测试工程101!

一旦算法被证明能够执行正确的操作,系统开发人员就可以将它下载到第一部机器人割草机样机中,并且对它作一系列测试,以便开发硬件平台。对硬件开发程序而言,算法在其中扮演了机器人测试向导的角色。

硬件子系统可能已经经过了基于PC的数据采集系统和控制系统的测试。但是,这些系统中的测试程序与AUD相比,只是拥有相同的硬件接口规范而已,在其他方面不具有相似性。而且,各个硬件子系统可能还没有协同工作过。因此,系统开发的最后一个步骤就是整合所有的子系统,并且统一调试。

系统集成最初可能是从在嵌入式单板计算机(SBC)上运行AUD开始的。这种计算机上运行的其实是用高级语言编写,并经过硬件仿真调试的相同程序。这是AUD首次对实际硬件实行控制。

这一阶段,许多软硬件接口以及软硬件自身的问题都会暴露出来。在嵌入式控制系统中,硬件与软件的关系非常紧密,以至于任何一处硬件或软件的改动都可能影响到对方。正是由于SBC具有机动性和可重复编程的特点,我们才选中它来实现完整的系统调试。

嵌入式控制系统设计师可以先利用FPGA对硬件设计作调试。然后,在产品产量允许的前提下,转而使用定制ASIC。

硬件实现

在我们解决了所有软件和硬件问题之后,就可以推出一款在外观和功能上都与最终产品十分接近的样品。ASIC与FPGA需要相同的引脚分布,它们都会被安装到一块小型母板上。母板可以支持任意一款引脚位置与之吻合的芯片。

如果我们采用FPGA,那么就需要在母板上额外增加一块程序存储芯片。这块芯片内存储了FPGA内部的互联信息。当我们把AUD下载到硬件之后,就会形成这些信息。FP

GA采用了动态RAM技术。这种技术的致命缺陷是具有易失性,FPGA内部运行的程序在断电之后会全部丢失。

这一阶段,系统开发人员可能会采用FPGA进行设计。因为FPGA版本的控制模块在引脚分布上可以做到与ASIC版本一致,而且FPGA还具有可重复编程的特点。FPGA的致命弱点同时也是它最受青睐的地方。因为在系统投入现场应用之前,开发人员很可能会对软件作升级。这样的话,如果我们只是为了升级ASIC程序就开发一款新产品,这样做在成本方面显然是行不通的。

即使我们的设计最终成为了一款产量达到千位数的标准产品,FPGA在经济性方面仍然具有优势。只有在产量达到几百万甚至更多的情况下,将AUD转换到ASIC所产生的大量NRE投入才可能被补偿掉。当然,对于消费类产品而言,这样的产量很快就能达到。

把AUD转换为适用于FPGA的HDL程序可能很困难也可能很简单。这一方面要看我们采用什么工具将已有的经过调试的软件转换为指定硬件的HDL代码,另一方面要看这种转换是在哪一阶段完成的。

例如,Mathworks正在与ASIC、FPGA供应商合作开发一套工具,帮助工程师将那些采用Matlab与Simulink编写的AUD代码转换为HDL,另有一些工具能够将C和C++代码转换为HDL。

当然,基本的测试表明,系统在经历任何重大改变之后,都必须重新作一遍开发测试。为了确保FPGA芯片下载了HDL代码之后确实能够执行原始AUD所指定的操作,我们必须做仿真和测试。当我们从FPGA编程转换到定制ASIC设计时,也会面临同样的问题。

翻译:翁思健

编辑精选

工控原创

- ▪ 春启智造新篇!2026年3月工业自动化资讯全览

- ▪ 当AI跨越虚实鸿沟,西门子如何在物理世界重写工业规则?

- ▪ 会造成工控系统失控等安全风险!工信部旗下单位发布工业领域OpenClaw应用风险通报

- ▪ ABB机器人携手英伟达 加速工业级物理AI规模化落地

- ▪ 舍弗勒宣布乐聚为首个中国具身智能合作伙伴,人形机器人走向全球产业协同

- ▪ 营收首破400亿欧元大关 施耐德电气2025财年交出强劲业绩

- ▪ 高效电机市场强劲复苏,2030年规模预计翻番至31亿美元

- ▪ 美的剥离伺服资产,聚焦核心部件突围

- ▪ 六十载创新积淀,ADI开启边缘智能新篇章

- ▪ “不拥抱就下岗”!朱兴明定调汇川技术2026年:全员AI化