白皮书|新型光链路提供完整的微波数据转换接口,保证系统范围的确定性

http://www.gkong.com 2022-08-09 09:58 来源:Teledyne e2v

试想一下,是否有可能使用光纤互联而不是铜线互联,建立多通道微波无线电系统?这种设计的优点包括:

- 通过光纤简化流采样、控制和配置数据,以及参考时钟和同步信号的无线电前端设计和信号分布,并减少线缆的重量

- 在未来的无线电设计中无需进行铜介质的信号布线,提供了更高的架构自由度和灵活性,同时减少了串扰和信道间干扰,从而获得更高的性能

- 光学概念证明可将前端模拟设计与后端数字信号处理分离,预示着由先进电子波束转向引领的增强操作全数字天线时代的到来

本文将详细介绍 Teledyne e2v 公司用于验证光链路假说的实验方法,并评估其发展现状。

如今,全球数据中心广泛地使用大量的光链路,因此乍一看这种光纤传输的设想可能不是特别具有创新性。右 边的方框里展示了使用光纤的主要优点。

光纤的优点

- 增强性能——没有串扰,EMI 为 0

- 长距离通信 >> 20 m

- 减少重量,提高信号密度

然而,在无线电设计的领域中,我们需要解决一些新的工程挑战。需要强调的是,这个方案旨在传输模拟信号环境和数字域的所有信号,因此必须处理低速控制信号和参考时钟分布,最关键的是,必须确保确定性的多通道同步。原因在于,如果要实现理想的电子波束转向,就必须保持信号空间(相位)的信息。

我们将讨论如何高效使用 FPGA 的数字资源实现实验数据编码和解码引擎的高级架构。我们还将详细介绍项目通常会遇到的挑战,以及如何维持系统范围里的确定性。好消息是这个方案已被证明是可行的。读者将深入了解这个 Teledyne e2v 新兴微波软件化能力的重要部分,之前的MWJ1文章首次讨论了这个问题。

1 能否通过光纤实现确定性数字相位阵列控制?, MWJ 2021 年 11 月

项目目标

到目前为止,有两个基于铜线的串行接口被用于连接宽带数据转换器和数字信号处理器。它们是行业标准JESD204 链接和 Teledyne e2v 的 无 需 许 可 证 的ESIstream 系统。

尽管光数据链路在现代的全球宽带应用中有广泛的应用,但迄今为止,在无线电前端设计领域中,很少有人努力用它取代传统的铜线设计。这里提出的数字光缆(ODH)项目旨在探索一种光学数据链路桥接的样机的能力和局限性,需保证 4 种系统信号的可靠传输。它们是:

- 参考时钟

- 所有频率小于 100MHz 的单端信号,包括 SPI 和通用 I/O(GPIO)

- 用于实现系统范围确定性采样的专利的同步信号

- 数据转换器的采样数据

在 Teledyne e2v 的数据转换器的领域中,确定性(即抑制不必要的伪随机亚稳态)通过一种被称为同步链的新型方法得以保证。同步链包含一个简单的单沿同步信号的分布和一个同步标志,使庞大的转换器并行系统保持同步。然而,使用铜介质时容易解决的问题,在使用光纤传输时变得更具挑战性。

我们设计了一种基于光纤的实验样机,以评估其作为铜线传输的替代品的适用性,并确定温度和其他环境因素对其性能的影响。

在最初的实验阶段,物理光纤链路的长度是 10 米,使微波射频模拟端和数字处理域分开适当的距离。

ODH实现

这个项目开始阶段的主要挑战有两点:

- 最重要的是保证相对慢速的控制信号的可靠传输

- 传输无错误的确定性同步信号至多个转换器,保证系统级确定性和同步采样。这一点目前仍在实验中。

先前的光纤链路的方案已支持控制信号和数据的传输。值得注意的是,英国林肯大学的一篇论文描述了一个基于 FPGA 的项目2,可组合 SPI 和 GPIO 数据并通过单一的光纤链路发送。

这篇论文描述了用于扩展传输距离的数据编码的方法,并阐述了面临的挑战。先前的结论是:

- 注意建立可靠的链路同步,需要主参考时钟。

- 编码是成功的关键因素。在所述的例子里,8b/10b编码被证明比其他更简单的编码方案(例如异或(XOR)或格雷码)更合适。

- 最后,如果延迟很重要,例如对于这个实验工作,作者详细说明了如何重新同步链路以补偿已知的系统延迟。

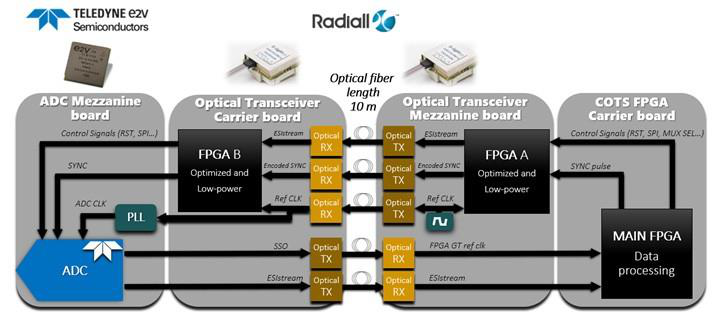

图 1 数字光缆的概念设计

之前的工作奠定了如今的样机的基石。我们提出了一种新的解决方案(图 1),将低成本、低功耗的可编程逻辑器件(这里是 FPGA)配置为简单的编码引擎,以格式化、聚合和序列化从系统 GPIO 和 SPI 消息直接生成的慢速控制向量。接着,编码的消息向量和参考时钟、离散编码的同步信号一起通过三路并行光学线路传输。

2 跨通道同步由于亚稳态而变得更加复杂。亚稳态是一种数字系统固有的伪随机行为,可通过精巧的设计来缓解。

实验实现

我们的样机基于现有的高端 IC 评估系统。我们选择了一个包含了 EV12AQ600 的高级微波前端板卡的系统。这款四通道、12 位 6.4Gsps 的宽带射频 ADC 支持最高6.4GHz 采样,为样机提供了基于 FMC 的目标 ADC。EV12AQ600 直接安装在一块强大的信号处理(DSP)板卡上,使用标准的 FPGA 板卡格式(FMC)连接器。FMC为现有的互联提供了有用的物理分隔,因此是改进的基于光纤的数字传输层的理想接口,如图所示。

考虑到所需的各种数字控制和时钟信号需通过 FMC 接口桥接,我们需要三个离散的光纤通道以控制发送到远程接收端 ADC 的信号。此外,我们还需要另外两个通道处理发回 DSP 板卡的数据和 SSO 通信。

我们的目标是实现一个实用的方案,因此需要寻找一款低成本、低功耗的可编程逻辑器件(PLD)。经过市场调研,Artix 7 FPGA 成为代码引擎的合适的选择。参考图 2 所示的系统分区,很明显对于未来的设计,可以很容易地将编码引擎资源和 DSP FPGA 合并以降低成本。目前,我们只使用了不到 5%的 Artix 7 的资源。这是一款易于使用的样机,可方便地进行编程,因此用户可在设计的早期阶段保持编码引擎为离散模块。

还需注意,我们需要远程访问参考时钟,因此样机的解码端需要一个本地的时钟发生器。物理层是通过 Radiall D-lightsys® VCSEL 光纤驱动器实现的。这个驱动器可支持从 100MHz 到 10GHz 的数据率,并在此范围内具有出色的时钟抖动性能。Radiall 的坚固耐用的 D 光组合提供三种数据率等级(10Mbps、5Gbps 和 12Gbps)和多个封装选项。这些器件被配置为四通道双工收发器或 12 通道单工接收器/发射器。驱动与协议无关,可提供标准LVDS 和 CML 电气接口。

两个关键的系统挑战

这款样机有两个核心挑战,它们是:

- 对非切换同步信号编码,以建立可靠的系统级光纤同步链解决方案,保证确定性

- 保证全速率链路锁定

提供系统范围的确定性同步

我们已在之前的几篇论文里介绍了同步链。如前所述,如果要完全用光介质替代铜介质,同步链是成功与否的关键因素。

在光纤上实现可靠的同步分布的挑战是,同步信号通常是一个相对慢速的信号,其逻辑电平变化大约为 10ns。考虑到同步信号的“无时钟”特性,它的精确的电平变化如何通过光纤传输?

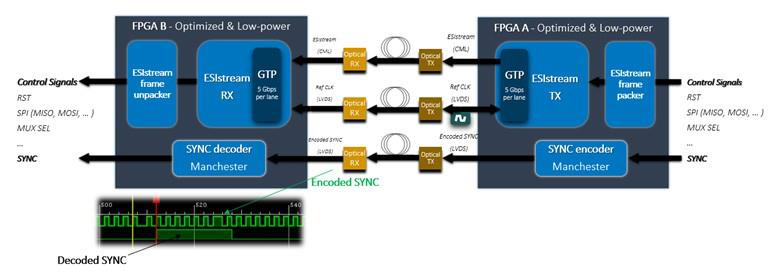

曼彻斯特编码是一种简单的相移键控技术,可提供一种合适的解决方案。二进制数据与时钟相位有关(图 2),可有效保证中位电平转换,有助于保持直流平衡(铜介质接口)并提供规律的数据边沿来源,以确保光纤链路保持锁定并可区分出 SYNC 的有效性。

图 2 SYNC 边沿的曼彻斯特编码

曼彻斯特编码容易通过异或(XOR)系统所需的 SYNC 信号和参考时钟实现。尽管这里可以看到在 SYNC 信号有效之前有一个稳定的零数据流,但在半个参考时钟周期内,接收端成功识别了 SYNC 由低到高的转变。

顺便说一句,延迟可能会影响系统级同步,这也是保证铜介质链接的确定性的挑战之一。使用光纤时,延迟比使用铜线时低几个数量级。因此,对于大多数的应用,调整多阵列系统中不同的 SYNC 传递时间变成了一个可以忽略的小问题。这是光纤解决方案的优点之一。

完全速率链接锁定

成功与否取决于两个因素。第一个因素是编码引擎的数字设计所固有的。此外,编码引擎依赖于嵌入式 PLL 以区分时钟沿和同步到参考时钟。

外部到编码引擎的部分与光纤链接的特性有关。在较大的数据率范围里,链路的性能有所不同。因此,光纤收发器需提供内部的电流调制控制。我们还未测试样机的这方面的特性,将在评估性能随温度变化的特性时进一步研究。

到目前为止的成果

尽管我们进行了大量的数字模拟,但还需在硬件就位并准备好上电后,进行实际的操作验证。也许尽管经过了一轮严格的检查,最初的设计还是存在一些微小的硬件错误,需要进一步修改和调整。

第一次上电令人失望。尽管我们进行了大量的模拟工作,但事实证明,寻找阻碍接收端锁定参考时钟的原因是一件非常具有挑战性的工作。我们开始怀疑接收的串行参考时钟的质量。当我们将参考时钟速率从 EV12AQ600标称的最大 12.8Gbps 线速率大幅降 低 至 9.0Gbps (4.5GHz 参考时钟),终于出现了令人期待的链接锁定。

虽然这时 ADC 输出数据速率只有期望最大值的三分之二左右,但令我们满意的是,我们已经建立了锁定的链路,未来可通过调整参考时钟和优化链接特性实现目标性能。在建立锁定的过程中,我们确认了几个关键的链接参数,从而验证了这个样机的核心假设,具体有以下几点:

- 多通道光纤链路解决方案可提供一个可行的结合了低速控制信号和高速数字信号的传输层

- 编码和解码解决方案需支持所需的所有接口信号需求,至少是当前光纤收发器正常工作所需的所有信号

- 关键的 SYNC 信号的成功编码和解码。这可为未来的相位阵列无线电设计提供支持。

- 光纤完全支持无线电模拟前端和数字信号处理后端的物理分隔

结论

尽快我们没有实现全速的数据信号,但这个使用超过 10米的光纤的实验设计已被证明是可靠的,虽然它的数据率比目标值低一些。此外,一旦建立了链接同步,样机就可不间断地运行,并且不会丢失链接锁定或改变比特错误率(BER)。更棒的是,我们使用 Radiall 光纤收发器 为光纤调制电流提数字控制,可进一步调整光纤传输特性。我们确信,通过进一步的优化,数据传输的能力会进一步增强,从而实现全速 12.8Gbps 的传输。

在我们宣称实验成功之前,有几个重要的问题需要进一步的验证。其中最重要的问题是验证更广泛的系统级确定性多通道操作的可行性,而不是简单的单接收的SYNC 解码。此外,这个问题的结论适用于不同的环境条件——特别是温度和电压变化的情况。

时间会证明一切,但至少迄今为止的进展是令人鼓舞的。现在,我们正站在向先进的数字智能微波天线设计的主要解决方案转变的边缘。

编辑精选

工控原创

- ▪ 思科工业AI报告:规模化落地全面提速 三大核心要素决定转型成败

- ▪ ADI:人形机器人爆发背后,连接与感知仍是关键挑战

- ▪ 春启智造新篇!2026年3月工业自动化资讯全览

- ▪ 当AI跨越虚实鸿沟,西门子如何在物理世界重写工业规则?

- ▪ 会造成工控系统失控等安全风险!工信部旗下单位发布工业领域OpenClaw应用风险通报

- ▪ ABB机器人携手英伟达 加速工业级物理AI规模化落地

- ▪ 舍弗勒宣布乐聚为首个中国具身智能合作伙伴,人形机器人走向全球产业协同

- ▪ 营收首破400亿欧元大关 施耐德电气2025财年交出强劲业绩

- ▪ 高效电机市场强劲复苏,2030年规模预计翻番至31亿美元

- ▪ 美的剥离伺服资产,聚焦核心部件突围