手动选择频段以缩短PLL锁定时间

http://www.gkong.com 2021-06-21 13:03 亚德诺

ADRF6820是一款高度集成的解调器和频率合成器,非常适合用于高级通信系统。 它内置一个宽带I/Q解调器、一个小数N/整数N分频锁相环(PLL)以及一个低相位噪声多核压控振荡器(VCO)。 该多核VCO覆盖2800MHz至5700MHz的基频范围。 本振(LO)输出范围为356.25 MHz至2850 MHz,可使用分频器(2分频、4分频和8分频)。

每个VCO内核包含多个重叠子频段,以覆盖数百MHz的频率范围。 将寄存器0x44中的位0和寄存器0x45中的位7均设为0,PLL可自动执行VCO频段校准并支持选择最佳VCO。

PLL锁定过程包括两个步骤:

- 通过内部环路自动选择频段(粗调)。 在寄存器配置期间,PLL首先根据内部环路进行切换和配置。 随后由一个算法驱动PLL找到正确的VCO频段。

- 通过外部环路细调。 PLL切换到外部环路。 鉴相器和电荷泵配合外部环路滤波器工作,形成一个闭环,确保PLL锁定到所需频率。 校准大约需要94,208个鉴频鉴相器(PFD)周期;对于一个30.72 MHz fPFD,这相当于3.07 ms。

校准完成后,PLL的反馈操作使VCO锁定于正确的频率。 锁定速度取决于非线性周跳行为。 PLL总锁定时间包括两个部分: VCO频段校准时间和PLL周跳时间。 VCO频段校准时间仅取决于PFD频率;PFD频率越高,锁定时间越短。 PLL周跳时间由所实现的环路带宽决定。 当环路带宽比PFD频率窄时,小数N分频/整数N分频频率合成器就会发生周跳。 PFD输入端的相位误差积累过快,PLL来不及校正,电荷泵暂时沿错误方向吸入电荷,使锁定时间急剧缩短。 如果PFD频率与环路带宽的比值提高,周跳也会增加;对于给定PFD周期,提高环路带宽会缩短周跳时间。

因此,当使用自动校准模式时,总锁定时间对某些应用来说可能太长。 本应用笔记提出一种通过手动选择频段来显著缩短锁定时间的方案,步骤如下:

- 按照表1所示的寄存器初始化序列使器件上电。 默认情况下,芯片以自动频段校准模式工作。 根据所需的LO频率设置寄存器0x02、寄存器0x03和寄存器0x04。

表1. 寄存器初始化序列

|

寄存器 |

值 |

|

0x00 |

0xfeff |

|

0x01 |

0x0041 |

|

0x02 |

0x0003 |

|

0x03 |

0x0020 |

|

0x04 |

0x0000 |

|

0x10 |

0x0c26 |

|

0x20 |

0x000a |

|

0x21 |

0x0082 |

|

0x22 |

0x0800 |

|

0x23 |

0x0002 |

|

0x30 |

0x1106 |

|

0x31 |

0x0900 |

|

0x32 |

0x0000 |

|

0x33 |

0x0a00 |

|

0x34 |

0x0010 |

|

0x40 |

0x000e |

|

0x42 |

0x0000 |

|

0x43 |

0x0002 |

|

0x45 |

0x0000 |

|

0x49 |

0x000f |

|

0x02 |

0x0000 |

|

0x03 |

0x0000 |

|

0x04 |

0x16bd |

- 读取锁定检测(LD)状态位。 若LD为1,表明VCO已锁定。

- 通过串行外设接口(SPI)回读寄存器0x46的位[5:0]。 假设其值为A,将系统中所有需要的LO频率对应的寄存器值保存到EEPROM。 由此便可确定频率和相关寄存器值的表格(参见表2)。

表2. 查找表

|

频率点 |

寄存器0x46 |

|

f1 |

A |

|

f2 |

B |

- 为缩短LD时间,将ADRF6820置于手动频段选择模式,并用第3步收集到的数据手动编程。 手动编程步骤如下:

- 将寄存器0x44设置为0x0001: 禁用频段选择算法。

- 将寄存器0x45的位7设为1,从而将VCO频段源设为已保存的频段信息,而不是来自频段计算算法。 用第3步记录的寄存器值设置寄存器0x45中的位[6:0]。

- 通过寄存器0x22的位[2:0]选择适当的VCO频率范围(参见表3)。

表3. VCO频率范围

|

LO选择 |

VCO频率范围(MHz) |

VCO_SEL(寄存器0x22的位[2:0]) |

|

内部VCO |

2850至3500 |

011 |

|

|

3500至4020 |

010 |

|

|

4020至4600 |

001 |

|

|

4600至5700 |

000 |

- 根据所需频率更新寄存器0x02、寄存器0x03和寄存器0x04。 寄存器0x02设置分频器INT值,即VCO频率/PFD的整数部分;寄存器0x03设置分频器FRAC值,即(VCO频率/PFD − INT) × MOD;寄存器0x04设置分频器MOD值,即PFD/频率分辨率。

- 监视LD以检查频率是否锁定。 例如,PFD = 30.72 MHz且LO = 1600 MHz。

表4. 手动频段校准寄存器序列

|

寄存器 |

值 |

描述 |

|

0x46 |

0x0032 |

读取频段校准值;LO = 1600 MHz的频段校准值 |

|

0x44 |

0x0001 |

禁用频段选择算法 |

|

0x45 |

0x00b2 |

将寄存器0x45的位7设为1以禁用自动校准,并迫使VCO使用所设置的频段值;位[6:0]必须载入之前记录的值 |

|

0x22 |

0x2A03 |

选择适当的VCO |

|

0x02 |

0x0034 |

INT |

|

0x03 |

0x0066 |

FRAC |

|

0x04 |

0x04cd |

MOD |

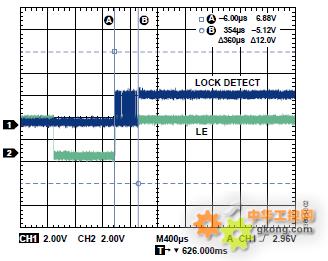

图1和图2分别显示了自动频段校准模式和手动频段校准模式下的锁定检测时间。 图2中,线1(锁定检测)上的高电平表示PLL已锁定。 线2 (LE)代表LE引脚,是一个触发信号。 注意:锁定检测时间必须从低到高读取。

自动频段校准模式下,锁定时间约为4.5 ms;手动频段校准模式下,锁定时间约为360 μs。 数据的测量条件为20 kHz环路滤波器带宽和250 μA电荷泵电流配置。

图1. 自动频段校准模式下的锁定时间,用信号源分析仪测试

图2. 手动频段校准模式下的锁定时间,用示波器测试

结论

利用手动频段选择,锁定时间从典型值4.5 ms缩短到典型值360 μs。 对于每个频率,首先利用自动频段选择确定最佳频段值并予以保存。 因为最佳频段值随器件而异,因此须对每个ADRF6820执行该程序。 VCO频段无需因为温度变化而更新。