��Ʒ�ص㣺

ΪFPGA �ܽŷ��䡢FPGA �������Ŵ�����PCB ��BGA ��װ�����Ż��ṩ�˼�����ƻ���

���FPGA�ܽŷ�����PCB���ֲ������֮���������ʹ������FPGA �ܽŵķ������Ż�������������

�Զ�����HDL Դ���롢FPGA �ܽŷ��估PCB ��BGA �����ܽ����ӹ�ϵ�ĸı䣬��ʾ������ݽ���ͬ������

֧������ڲ�ͬFPGA ����֮�����ֲ

�ɽ��PCB �����Ż�FPGA �����Ĺܽŷ��䣬֧�ֹܽŷ�����Ϣ��IO Designer��

ԭ��ͼ��PCB �����е�˫��

֧������FPGA ���ҵ������⣬���ݸ���FPGA �����������ۺ�Լ���ļ������ֲ���Լ���ļ����ɵ�����Ż����еĹܽŷ�����Ϣ

I/O Designer�����Զ������ĵ��ӱ�����ͼ�δ��ڹ��ɵ�FPGA/PCB ������ƻ�������

FPGA/CPLD �ڵ��Ӳ�Ʒ����е�Ӧ�ü���㷺����FPGA ��PCB ��ͬ������ѳ�Ϊҵ���ձ����ٵ����⡣��ƹ���ʦ��ҪͶ�������ʱ�䣬������ͨ��ȷ�϶�FPGA �ܽŷ�����Ϣ���ģ�������©������FPGA �ܽŶ�����PCB �������ӵ����ݲ�һ�£��Ӷ���ɲ�Ʒ�������ڵ�������Ʒ���������FPGA ������ģ������/�ܽ����������ӣ�ijЩ�����ܽ����Ѵ�1500 �����ϣ�FPGA ��PCB ��ͬ�������������ͻ����

Mentor Graphics ��˾��I/O Designer ��ҵ���������FPGA/PCB ͬ����ƵĽ��������

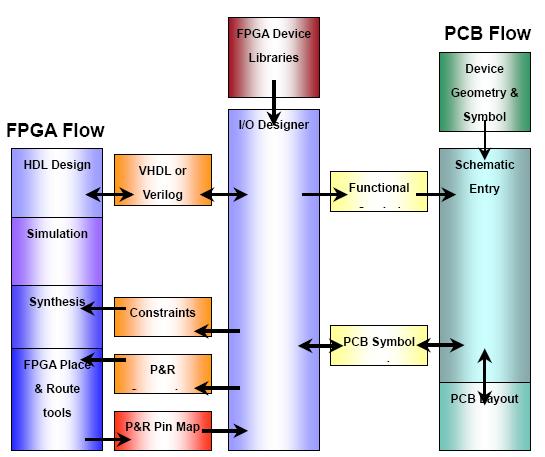

��I/O Designer �ļ��ɻ��������߿��Ե���HDL ����е��źš�FPGA �����Ĺܽ���Ϣ�����Լ����Ϣ��ԭ�� ͼ���š�PCB ������ͼ���������ӵȹؼ���Ϣ��Ȼ���ֹ����Զ�����HDL �źŵ�FPGA �ܽŵ�ӳ�䡢�Զ���������FPGA ������ԭ��ͼ���ź����硢����PCB���ֺ�����������ͼ���������Ż�FPGA �ܽŷ��䡢�����Ż���Ĺܽŷ���������FPGA �ۺ�Լ���Ͳ��ֲ���Լ����ȷ������ŶӸ�Ч�ʡ��ͷ��յ�ʵ��FPGA/PCB ��ͬ����ơ�

��̬�ܽŷ������Ż�

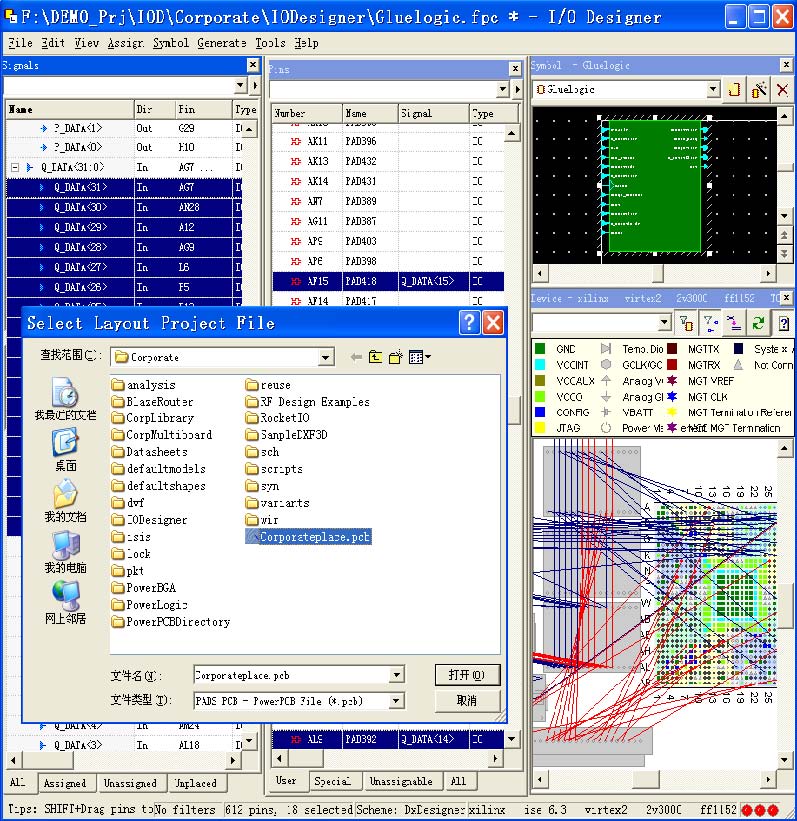

I/O Designer Ϊ�������Ż�FPGA �ܽŷ����ṩ�˼��ֱ�۵IJ������棬����߿ɶ���ù���Ȼ��ͨ������ΪHDL �ź��Զ�����FPGA �ܽţ�Ҳ��ͨ��������зŲ���ʵ�ֵ�һ�źŻ����ߵ�FPGA �ܽŵ�ӳ�䡣�����������������PCB ������ͼ������ֱ�ӿ���PCB ��������߽���״�������Դ����Զ����ֹ��Ż�FPGA �ܽŵķ��䣬ÿ���Ĺܽŷ����Ч�������������ж�̬ʵʱ����ʾ������߿��Կ��ٶ�ȷ�����FPGA �ܽ��Ż�������

����ͬ��������FPGA ��PCB ����������HDL�ź���FPGA �ܽŵ�ӳ����Ϣ�����ϸ�һ�¡�I/O Designer �����Զ����ٸ������̶Թܽŷ�����Ϣ���ģ�����ʾ�������̼�ʱ���£�ȷ���ܽŷ�����Ϣ��������������е�һ���ԡ����ȣ�I/O Designer ֧���ֹ����Զ����HDL�źŵ�FPGA �ܽŵ�ӳ�䣬������ӳ��������FPGA ���ֲ���Լ���ļ���Ȼ����HDL Դ�ļ��������ڰ弶��Ƶ�ԭ��ͼ���š�Ԫ�����Լ��ܽ����Ե���Ϣ�����⣬I/O Designer �����Ե���弶ԭ��ͼ��PCB ����жԹܽŷ�����IJ�������ܽŻ�����Pin Swap�������Ż�����GateSwap���ȣ��Ӷ�����FPGA ���ֲ���Լ����

����FPGA/PCB ��ͬ����ƣ�I/ODesigner ��һ������ǿ���Ҷ�һ���Ľ����������Ϊ��FPGA ���ֲ��ߡ�Լ���ļ� ���弶PCB ��ơ��ṩ��ǿ������˫�����ݽ�������������߿���ͨ��I/O Designer ����HDL �źš�ԭ��ͼ���š�PCB ���߹��ܽŵ�����Ϣ��FPGA ���ֲ���Լ���ļ��ȶ������ݣ������ݸ�HDL��FPGA ���ֲ��ߡ�PCB �ȸ���������̣���Ч��ʵ���˴Ӹ�����ơ�оƬ��Ƶ�ϵͳ��Ƶ����νӡ�

���̲�Ʒ�з�����I/O Designer ������ȷ��FPGA ��PCB������Ƶ�˳�����У����Դ�������̲�Ʒ�з����ڡ���FPGA ��PCB ������ƹ����У���ʹijһʱ��FPGA �ܽŷ����Ѿ�ȷ������������Ŀ�Ľ�չ��FPGA ����ʦ��PCB����ʦ��ʱ�����ܸ����Լ�����Ҫ�Ĺܽŷ��䣬������������ܳ�����

����Ƴ��ڡ���Ʒ���Լ��Ľ��Σ���ijЩģ�鹦�ܵ����¶���ᵼ���źŵĸı䣬��ȻӰ��ܽŷ���;

HDL ����ı����Ҫ��FPGA ���²��ֲ��ߣ�ԭ�еĹܽŷ��䱻����;

��PCB ���ʱ��Ϊ�˸���BGA ��װ�IJ��߶�Ƶ�����е����ڹܽ�����Ի���������ʹFPGA �ܽŷ������I/O Designer �����Զ����ÿλ��Ƴ�Ա�Թܽŷ�����ģ���������Ϣ���ݸ�������Ա���ڵõ�����������Զ��� ������Ա�����ݽ��и��£�ȷ���ܽ����źŵ�ӳ����Ϣ��FPGA ��PCB ����������ϸ�һ�¡�

ԭ��ͼ�����

I/O Designer �Դ�һ���ɶ��Ƶ�ԭ��ͼ���ţ�Symbol����ܽţ�Pin�����ο⣬֧�����кϺ���ҵ����IEEE/JEDEC���Ĺܽ���š�Symbol ��Pin �����ε���Ϣ������߿��Ը�����Ҫ����Symbol ��Pin ����״��

I/O Designer ���ݶ����ļ���ʽ��ԭ��ͼ��Symbol���ɽ��Լ�������ԭ��ͼ��Symbol������Design Architect��Board Archite��DxDesigner��Design Capture��Design View�Ȼ����У�ͬʱ֧��EDIF��XML �ȸ�ʽ��ԭ��ͼ��Symbol �ļ��ĵ��롣