|

作者:李鹏 上官瑞春 曹磊 相朋举

(北京泛华恒兴科技有限公司,北京 100192 )

引言

航天测控设备经常工作在强振动、高噪音、粉尘多,温度变化大的恶劣环境中。因此,其内部电子设备间的数据通信要求通过严格的故障检测,以达到较高的可靠性、残存性和容错能力。在实时性方面,动力系统一体化控制要分别对发动机和变速器进行控制,二者之间的数据通信要求一条消息的最大响应时间一般极短,这样才能实现对发动机和变速器的实时控制,从而提高整个动力系统的综合性能。此外,还有一些对数据通信的特殊要求,如协议简单性、短帧信息传输、信息交换的频繁性、网络负载的稳定性、高安全性和性价比高等。

为此,本文提出了一种基于PXI总线和1553B总线的高精度同步测控技术,在实时操作系统下实现总线通信与模拟信号发送、采集同步启动,同时提供了某型动力系统一体化设备高可靠性和实时性测控解决方案。

1 系统总体方案

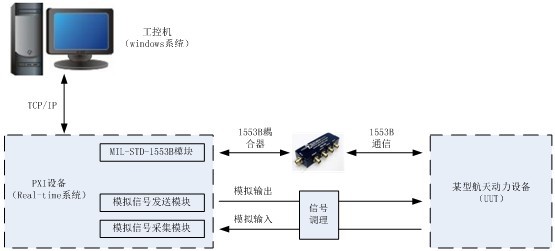

整体系统组成结构如下图所示

图 1系统结构示意图 图 1系统结构示意图

系统基于1553B总线通信模块和PXI总线模拟信号输入输出测试设备,用于某型动力设备的控制与反馈测试的研究性实验。测试项目主要包括零位检测、极性检测、位置特性测试、暂态特性测试、频率特性测试。各项测试都需要1553B总线通信与模拟输出输入控制同步开始。系统具备模拟信号接口和1553B总线接口,利用 1553B总线发送周期指令信号及数据信号,同时接收遥测信号以及命令反馈信号;通过模拟信号向被测组件发送控制调节指令信号,同时接收位置反馈信号以及其他模拟信号,并且可以进行数据分析及性能测试。

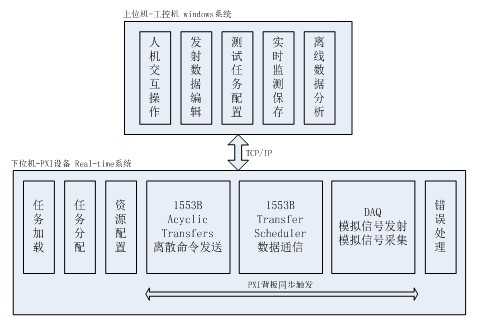

整体系统功能模块框图设计如下图所示。

图 2系统功能模块框图

该系统从结构上可分为上位机和下位机两部分:

(1)上位机运行于WINDOWS系统下,主要功能:

- 人机交互

- 测试项管理

- 波形文件编辑

- 数据显示、保存

- 总线数据监测

- 离线数据算法分析(位置特性、暂态特性、频率特性)

(2)下位机建立在基于PXI的硬件平台上,运行于Real-time操作系统下,主要功能:

- 测试项加载

- 测试任务分配

- 物理测试资源配置

- 1553B模块和CAN模块离散通信指令下发

- 1553B模块硬件定时连续数据通信

- 1553B总线通信与DAQ模块同步触发

- 错误处理与记录

2 系统关键技术

2.1 1553B总线功能模块设计

2.1.1 硬件定时与数据无缝加载

1553B硬件定时数据通信,通过Transfer Scheduler模块设计,系统Minor Frame Time为1ms。即1ms硬件定时时间内,完成1553B总线的BC-RT以及RT-BC通信。硬件定时误差±1μs。

图 3 Transfer Scheduler模块

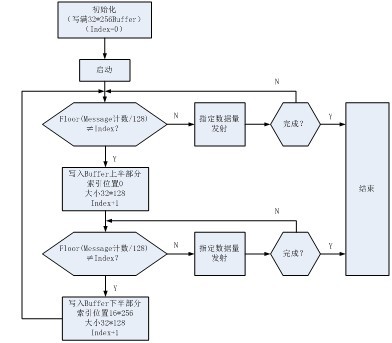

数据通信过程中,硬件定时1ms完成一次1553B总线的数据传递,那么准确有效的加载发射数据尤为关键。系统设计了深度为256的Buffer空间(大小为32*256),初始化时写满启动数据, Message开始计数,对应从Buffer索引0或者Buffer索引16*256的位置写入32*128个数据;如此反复切换写入直至数据全部发送完成,从而实现了1553B数据无缝加载。其程序流程算法如下图所示。

图 4数据无缝加载算法流程图

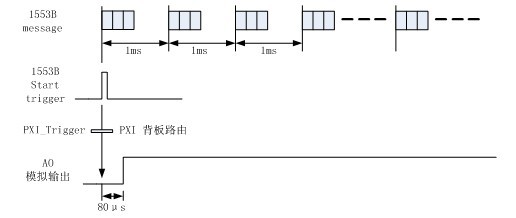

2.1.2 同步触发DAQ数据采集模块

通过Acyclic Transfers模块设计了Strobe触发帧,通过PXI总线背板的PXI_Trigger接口将触发信号路由至DAQ模块触发源接口,利用“DAQ开始触发”配置,实现了1553B总线通信数据与DAQ数据发射/采集同步进行的功能,同步精度±80μs。

图 5 Strobe触发帧

如下图所示,利用1553B的异步帧,发送1553B Start trigger至PXI背板PXI_Trigger,触发模拟信号发送。关于80μs延迟,由信号切换、路由时间以及模拟信号模块D/A转换速率等多方面因素影响,可以通过专用的模拟信号同步模块进一步提升系统整体的同步精度。

图 6 1553B触发同步开始

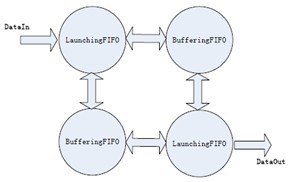

2.2 Real-Time操作系统下数据缓冲设计

为了避免同一个数据文件读取多次,降低Real-Time 操作系统下内存、CPU 使用率以及硬件操作,设计了PingPangFIFO数据缓冲机制,其实现原理如下图所示:

图 7 PingPangFIFO数据缓冲机制

每个文件数据读入到LaunchingFIFO 中后,其镜像的BufferingFIFO 也会备份同样的数据, 由此两个FIFO 通过PingPang 缓冲的机制,循环对外输出一份完整的文件数据到硬件发射板卡上DA,进行数据发射,实现了同一个数据文件定时循环多次发射,而不必反复执行文件IO 的操作,有效提高了系统的可靠性,延长了硬盘使用寿命,降低了CPU 使用率。

该技术优势在于每个发射文件只需要读取一次即可;只要内存允许,可以完成上百兆数据大小的发射;避免反复进行硬件配置操作;保证了多次反复发射之间数据和时间上的严格连续。

2.3 系统容错处理与故障恢复设计

考虑到整体系统的高可靠性要求,基于Real-Time操作系统下设计了系统容错处理与故障恢复机制。根据系统报错类型的不同,设定对应的容错等级。如系统的某块PXI板卡驱动报错,则系统先重置该线程,之后重置板卡获取对应的反馈信息做相应的容错处理并单独设定线程做故障记录,以便于后期检修和维护。 另外在系统软件关键线程上添加看门狗,用来监控核心线程实时情况,在必要时启动看门狗以重新板卡和系统,恢复初始状态,从而在不影响系统功能情况下根据系统时间自动加载新的任务,使得操作人员不必实时监控与维护系统,提高了设备智能化程度。

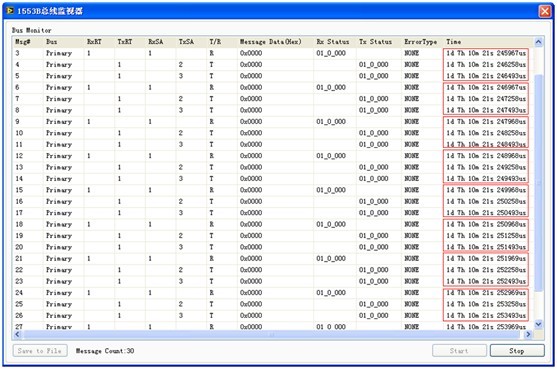

3 测试结果与分析

经过多次反复测试,由下图可见该系统完成了通信帧时间1ms硬件定时,误差±1μs。

图 8 总线监视器

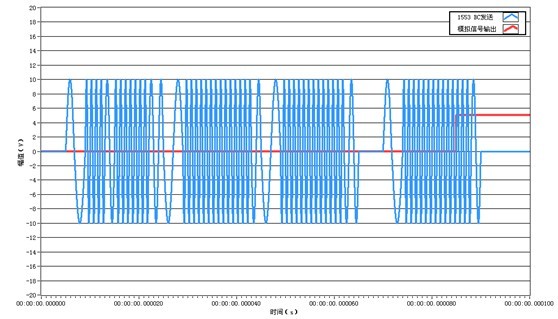

1553B异步Strobe触发帧,实现了1553B总线通信与DAQ模拟数据发射、采集同步开始,同步误差80μs,可以通过专用的模拟信号同步模块进一步提升系统整体的同步精度。测试结果如下图所示。

图 9 同步信号数据分析

4 结论

综上所述,本文提出的基于PXI总线和1553B总线的测控技术,1553B总线的命令/响应的协议方式保证了实时的可确定性,合理的拓扑结构使得1553B总线成为分布式设备的理想连接方式。该系统完成了通信帧时间1ms硬件定时,误差±1μs;同时通过1553B异步Strobe触发帧,实现了1553B总线通信与DAQ模拟数据发射、采集同步开始,同步误差正负80μs;同时实时系统数据缓冲技术提高了系统使用效率,降低了内存与CPU的消耗,设计了系统容错与故障恢复,保证系统长期运行的稳定性,提高了整个系统的可靠性,且易于操作及扩展。目前该系统设备已投入实际使用中,运行良好。

|