产品特点:

为FPGA 管脚分配、FPGA 器件符号创建及PCB 中BGA 封装网络优化提供了集成设计环境

搭建在FPGA管脚分配与PCB布局布线设计之间的桥梁,使繁琐的FPGA 管脚的分配与优化工作变得轻而易举

自动跟踪HDL 源代码、FPGA 管脚分配及PCB 中BGA 器件管脚连接关系的改变,提示相关数据进行同步更新

支持设计在不同FPGA 器件之间的移植

可结合PCB 网表优化FPGA 器件的管脚分配,支持管脚分配信息在IO Designer、

原理图和PCB 环境中的双向传递

支持所有FPGA 厂家的器件库,兼容各种FPGA 开发环境的综合约束文件、布局布线约束文件,可导入或优化其中的管脚分配信息

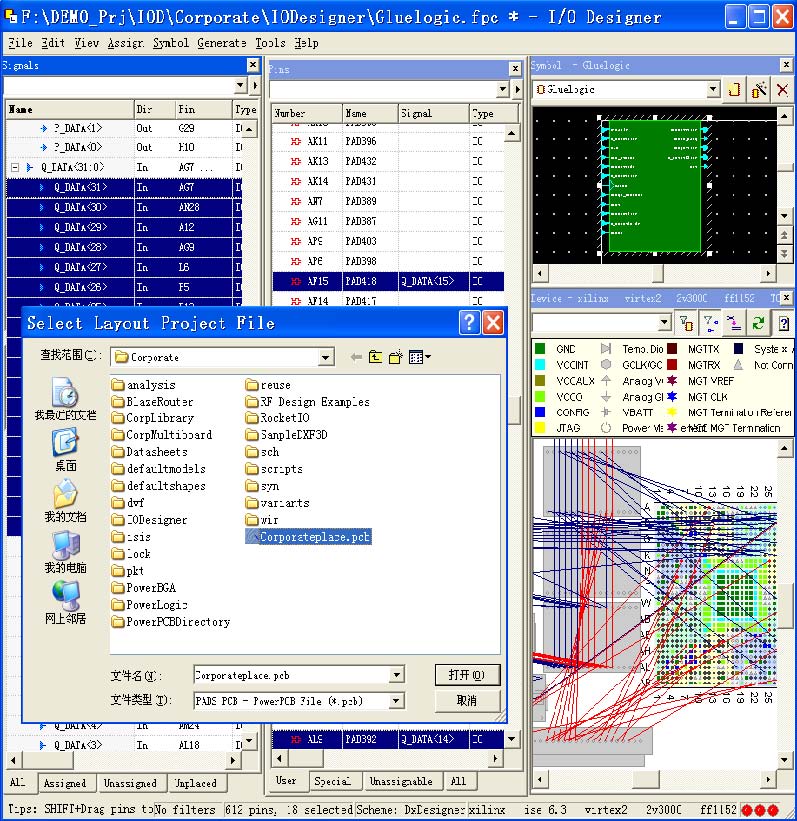

I/O Designer:由自动关联的电子表格与图形窗口构成的FPGA/PCB 集成设计环境概述

FPGA/CPLD 在电子产品设计中的应用及其广泛,而FPGA 与PCB 的同步设计已成为业界普遍面临的难题。设计工程师们要投入大量的时间,反复沟通和确认对FPGA 管脚分配信息的修改,稍有疏漏便会造成FPGA 管脚定义与PCB 网络连接的数据不一致,从而造成产品开发周期的延误及设计反复。随着FPGA 器件规模(门数/管脚数)的增加,某些器件管脚数已达1500 个以上,FPGA 与PCB 的同步设计问题愈加突出。

Mentor Graphics 公司的I/O Designer 是业界最优秀的FPGA/PCB 同步设计的解决方案。

在I/O Designer 的集成环境里,设计者可以导入HDL 设计中的信号、FPGA 器件的管脚信息与设计约束信息、原理 图符号、PCB 布局视图与网络连接等关键信息,然后手工或自动创建HDL 信号到FPGA 管脚的映射、自动创建复杂FPGA 器件的原理图符号和网络、参照PCB布局和网络连接视图来调整和优化FPGA 管脚分配、根据优化后的管脚分配来更新FPGA 综合约束和布局布线约束,确保设计团队高效率、低风险地实现FPGA/PCB 的同步设计。

动态管脚分配与优化

I/O Designer 为创建与优化FPGA 管脚分配提供了简洁直观的操作界面,设计者可定义好规则,然后通过软件为HDL 信号自动分配FPGA 管脚,也可通过简单的鼠标托放操作实现单一信号或总线到FPGA 管脚的映射。设计者还可以在软件的PCB 布局视图窗口中直接看到PCB 中网络飞线交叉状况,并以此来自动或手工优化FPGA 管脚的分配,每次修改管脚分配的效果都能在软件中动态实时地显示。设计者可以快速而准确的完成FPGA 管脚优化工作。

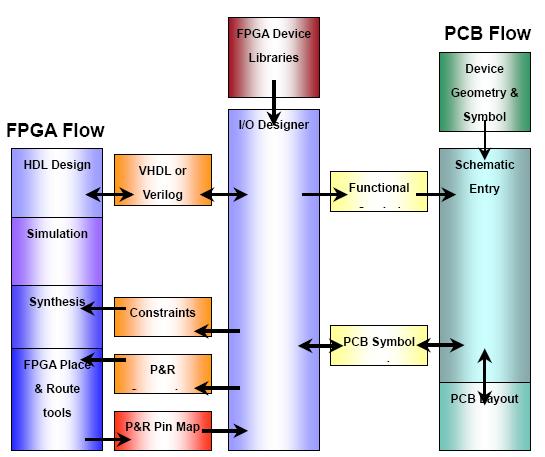

数据同步管理在FPGA 到PCB 的设计流程里,HDL信号与FPGA 管脚的映射信息必须严格保持一致。I/O Designer 可以自动跟踪各个流程对管脚分配信息的修改,并提示其他流程及时更新,确保管脚分配信息在整个设计流程中的一致性。首先,I/O Designer 支持手工或自动完成HDL信号到FPGA 管脚的映射,并根据映射结果创建FPGA 布局布线约束文件,然后结合HDL 源文件生成用于板级设计的原理图符号、元件属性及管脚属性等信息;此外,I/O Designer 还可以导入板级原理图或PCB 设计中对管脚分配的修改操作,如管脚互换(Pin Swap)、逻辑门互换(GateSwap)等,从而更新FPGA 布局布线约束。

对于FPGA/PCB 的同步设计,I/ODesigner 是一个功能强大且独一无二的解决方案,它为“FPGA 布局布线—约束文件 —板级PCB 设计”提供了强有力的双向数据交换环境,设计者可以通过I/O Designer 创建HDL 信号、原理图符号、PCB 布线规则、管脚电气信息、FPGA 布局布线约束文件等多种数据,并传递给HDL、FPGA 布局布线、PCB 等各个设计流程,有效地实现了从概念设计、芯片设计到系统设计的无缝衔接。

缩短产品研发周期I/O Designer 还可以确保FPGA 与PCB并行设计的顺畅进行,可以大幅度缩短产品研发周期。在FPGA 与PCB 并行设计过程中,即使某一时刻FPGA 管脚分配已经确定,但随着项目的进展,FPGA 工程师或PCB工程师随时都可能根据自己的需要修改管脚分配,以下三种情况很常见:

在设计初期、产品调试及改进阶段,对某些模块功能的重新定义会导致信号的改变,必然影响管脚分配;

HDL 代码改变后,需要对FPGA 重新布局布线,原有的管脚分配被打乱;

在PCB 设计时,为了改善BGA 封装的布线而频繁进行的相邻管脚网络对换操作,迫使FPGA 管脚分配调整I/O Designer 可以自动监测每位设计成员对管脚分配的修改,并将修改信息传递给其他成员,在得到允许后可以自动对 其他成员的数据进行更新,确保管脚与信号的映射信息在FPGA 与PCB 设计流程中严格一致。

原理图与符号

I/O Designer 自带一个可订制的原理图符号(Symbol)与管脚(Pin)外形库,支持所有合乎工业标准(IEEE/JEDEC)的管脚序号、Symbol 及Pin 的外形等信息,设计者可以根据需要订制Symbol 及Pin 的形状。

I/O Designer 兼容多种文件格式的原理图与Symbol,可将自己创建的原理图及Symbol导出至Design Architect、Board Archite、DxDesigner、Design Capture、Design View等环境中,同时支持EDIF、XML 等格式的原理图及Symbol 文件的导入。